长裕建设有限公司网站查询网站域名

文章目录

- 前言

- 一、数据位宽

- 1、有符号定点数

- 2、Nbit和Mbit相加或相乘

- 二、阻塞赋值和非阻塞赋值

- 三、timescale

- 四、三态门的设计

- 五、verilog模块编程原则

- 六、二进制码、独热码、格雷码比较

- 1、独热码

- 2、格雷码

- 3、二进制码

前言

2023.4.5 清明节

一、数据位宽

N位有符号数:-2^(N-1) ~ 2^(N-1) -1

N位无符号数:0 ~ 2^N-1

如:8bit无符号数范围0-255,有符号数范围-128-127(0占掉了正数)

1、有符号定点数

范围:

最大值:3 + 2^-1 + 2^-2 + 2^-3 + 2^-4

最小值:-4 - (2^-1 + 2^-2 + 2^-3 + 2^-4 +2^-5)

N = 8,3Q5 //总共8位数,整数部分3位,小数部分5位

2、Nbit和Mbit相加或相乘

相加位数:+1

相乘位数:N+M

二、阻塞赋值和非阻塞赋值

组合电路要使用阻塞赋值,时序电路使用非阻塞赋值

| 阻塞赋值 | 非阻塞赋值 |

|---|---|

| = | <= |

| 立刻执行,立刻改变 | 一个周期计算右边的值,下个周期赋值给左边,在过程块结束时才完成赋值操作 |

| 执行过程不受其他语句执行的影响 | 不影响其他语句的执行 |

| 其他语句在执行后顺序执行 | 并行执行 |

| 在串行语句块中,顺序执行;在并行语句块中,同时执行 | 在串行语句块中,执行没有先后之分,各条语句并行执行 |

三、timescale

- 时间精度要小于等于时间单位

- 只能是1、10、100这样的数

- verilog是没有默认的timescale,没有声明的模块可能会错误的使用前面模块的定义

`timescale 时间单位/时间精度

`timescale 1ns/1ps

四、三态门的设计

三态门:既不是0,也不是1,电阻很大,相当于开路

always@(din or en)beginif(en)dout = din;elsedout = 1'bz;

end//或者assign赋值

assign dout = en ? din : 1'bz;

五、verilog模块编程原则

- 时序电路建模时,用非阻塞赋值。

锁存器电路建模时,用非阻塞赋值。- 用always块建立组合逻辑模型时,用阻塞赋值。

- 在同一个always块中建立时序和组合逻辑电路时,用非阻塞赋值。

- 在同一个always块中不要既用非阻塞赋值又用阻塞赋值。

- 不要在一个以上的 always 块中为同一个变量赋值。

- 用

$strobe系统任务来显示用非阻塞赋值的变量值。 - 在赋值时不要使用#0延时。

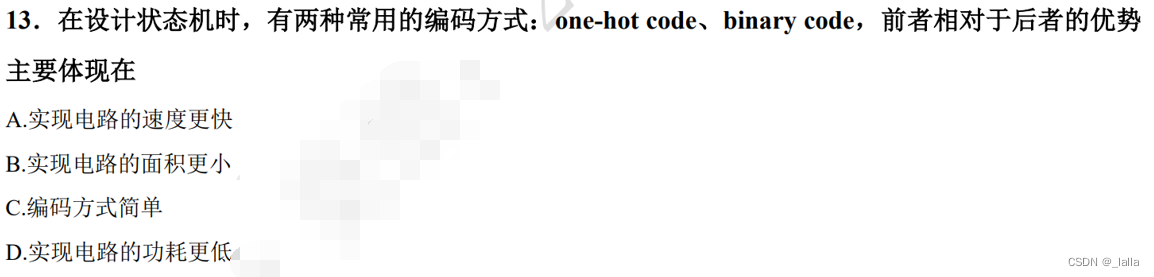

六、二进制码、独热码、格雷码比较

1、独热码

一种使用N位状态寄存器来对N个状态进行编码的方法,每个状态都由它独立的寄存器位,并且在任意时候,其中只有一位有效。

-

优点:状态比较时仅需要比较一位,从而在一定程度上简化了译码逻辑,节约了组合逻辑资源,速度更快 -

缺点:需要较多的寄存器资源,且编码效率低,适合用于状态数较少的情况。

2、格雷码

每次只有一位发生变化的二进制编码方法

优点:每次只改变1bit,低功耗,发送亚稳态概率降低缺点:无权码,不能直接进行计算

3、二进制码

编码简单,可以进行运算,但是翻转较多,容易产生亚稳态