郑州网站建设公司前景站长之家排行榜

前言:本章内容主要是演示Vivado下利用Verilog语言进行电路设计、仿真、综合和下载

示例:计数器与分频器

- 功能特性: 采用 Xilinx Artix-7 XC7A35T芯片

- 配置方式:USB-JTAG/SPI Flash

- 高达100MHz 的内部时钟速度

- 存储器:2Mbit SRAM N25Q064A SPI Flash(样图旧款为N25Q032A)

- 通用IO:Switch :x8LED:x16Button:x5DIP:x8 通用扩展IO:32pin

- 音视频/显示: 7段数码管:x8 VGA视频输出接口 Audio音频接口

- 通信接口:UART:USB转UART Bluetooth:蓝牙模块

- 模拟接口: DAC:8-bit分辨率 XADC:2路12bit 1Msps ADC

目录

Ⅰ. 前置知识

0x00 二进制计数器

0x01 利用IP核构造计数器

Ⅱ. Verilog实现

0x00 分频器

0x01 时序约束

Ⅰ. 前置知识

0x00 二进制计数器

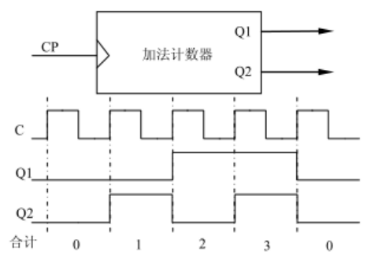

一个简单的二进制计数器通过二进制序列反复循环实现计数。以两位加法计数为例,每次时钟脉冲信号clk 为上升沿时,计数器会将计数值加1。所以计数值(由Q1Q0组成),依次是 00,01,10,11,00,11…,周而复始。在图中的波形图里,透露了这样几个信息:

[i] 一个两bit计数器,它所能计数的范围是 0~3(即22-1)。同理,n bits的计数器所能计数的范围是0~2n-1。

[ii] 如果将Q0、Q1作为单独信号线引出,由Q0、Q1得到的波形频率是时钟脉冲信号clk的1/2、1/4,亦即是将时钟脉冲信号的clk频率除2、除4。因此图示计数器又常被称为除4计数器。

[iii] 由上讨论推广可知,n bits计数器可获得的信号之多是频率除2n的结果。

参考如下源程序,试分析其分频系数:

1.

module addcounter(clk,Q) ;

input clk ;

output[1:0] Q ;

reg[1:0] Q ;

always @(posedge clk)begin

Q<=Q+1 ;

end

endmodule2.

module counter3(clr,clk,Q)

input wire clr; input wire clk;

output reg[2:0] Q;

input wire [2:0] D;

assign D[2] = ~Q[2] & Q[1] & Q[0] | Q[2] & ~Q[1] | Q[2] & ~Q[0]

assign D[1] = ~Q[1] & Q[0] | Q[1] & ~Q[0]

assign D[0] = ~Q[0]

always @ (posedge clk or posedge clr) beginif(clr==1) Q<=0;else Q <=D

end

endmodule通用型的二进制计数器一般具备更多功能,例如可以增/减计数、预置初值、同步清零、暂停等。74LS161就是一种常用的可预置4位二进制同步加法计数器。其功能表如下图表:

| 输入 | 输出 | |||||||||||

| P | T | CP | D0 | D1 | D2 | D3 | Q0 | Q1 | Q2 | Q3 | ||

| 0 | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | 0 | 0 | 0 | 0 |

| 1 | 0 | Ⅹ | Ⅹ | ↑ | D0 | D1 | D2 | D3 | D0 | D1 | D2 | D3 |

| 1 | 1 | 1 | 1 | ↑ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | 计数 | |||

| 1 | 1 | 0 | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | 保持 | |||

| 1 | 1 | Ⅹ | 0 | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | 保持 | |||

0x01 利用IP核构造计数器

(1)根据上述74LS161的原理和参考代码,在vivado中设计计数电路:

module CNT161( input CR, input CP, input [3:0] D , input LD, input EP, input ET, output wire [3:0] Q);

wire [3:0] Din;

reg [3:0] Dout;

assign Din=D;

assign Q=Dout;

always@(posedge CP or negedge CR) begin

if (CR==0) Dout<=0;

else if (LD==0) Dout<=Din;

else if (LD==1 && EP==0 && ET==0) Dout<=Dout;

else if (LD==1 && EP==0 && ET==1) Dout<=Dout;

else if (LD==1 && EP==1 && ET==0) Dout<=Dout;

else if (LD==1 && EP==1 && ET==1) Dout<=Dout+1;

end

endmodule (2)实验板时钟为100MHZ,利用计数器构造分频输出1H:

module slowClock(clk, reset, clk_1Hz);

input clk, reset;

output clk_1Hz;

reg clk_1Hz = 1'b0; // provide initial condition for this register.

reg [27:0] counter;

// counter size calculation according to input and output frequencies

parameter sys_clk = 100000000; // 50 MHz system clock

parameter clk_out = 1; // 1 Hz clock output

parameter max = sys_clk / (2*clk_out); // max-counter size

always@(posedge reset or posedge clk) beginif (reset == 1'b1) beginclk_1Hz <= 0;counter <= 0;endelse begincounter <= counter + 1;if ( counter == max) begincounter <= 0;clk_1Hz <= ~clk_1Hz;endend

end

endmodule Ⅱ. Verilog实现

0x00 分频器

设计代码:

module slowClock(clk, reset,Q);input clk, reset;output [3:0] Q;reg [3:0] Q = 4'b0000;// provide initial condition for this register.reg [27:0] counter;// counter size calculation according to input and output frequencies

parameter sys_clk = 1;

parameter clk_out = 1;

parameter max = sys_clk / (2*clk_out); // max-counter sizealways@(posedge reset or posedge clk) beginif (reset == 1'b1) beginQ <= 0;counter <= 0;endelse begincounter <= counter + 1;if (counter == max) begincounter <= 0;Q<=Q+4'b0001;endendend

endmodule❗ 注:

parameter sys_clk = 1;

parameter clk_out = 1;

parameter max = sys_clk / (2*clk_out); // max-counter size

是根据EGO1板子的频率编写的,不同的板子可用设置不同的分频

仿真代码:

module sim_slowClock();reg clk ,reset;wire [3:0] Q;slowClock test(.clk(clk),.reset(reset),.Q(Q));initial clk=0;initial reset=1;always begin#10;clk=~clk;reset=0;end

endmodule

在Vivado中点击”RTL ANALYSIS->Open Elaborated Design”,可以查看综合得到的逻辑电路,如图所示:

仿真代码:

- 从图中可以看出上升沿有效且为异步电路;

- reset高电平有效,一开始为1,进行置数,置为0000;

- 从波形图可以看出为十六分频;

0x01 时序约束

由于需要时钟信号,所以还要进行时序约束。

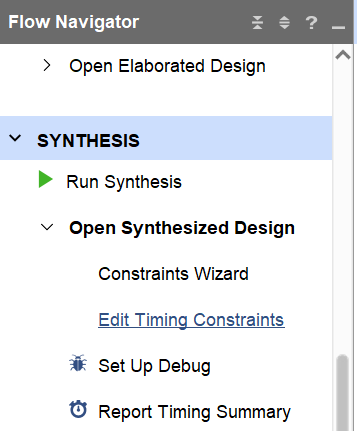

【a】选择在Flow Navigator 中选择Synthesis > Synthesized Design > Edit Timing Constraints。

【b】打开时序约束界面,开始进行时序约束。

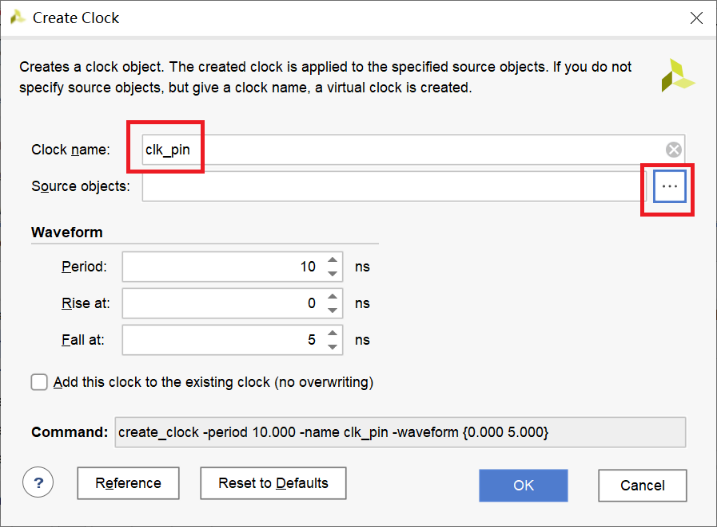

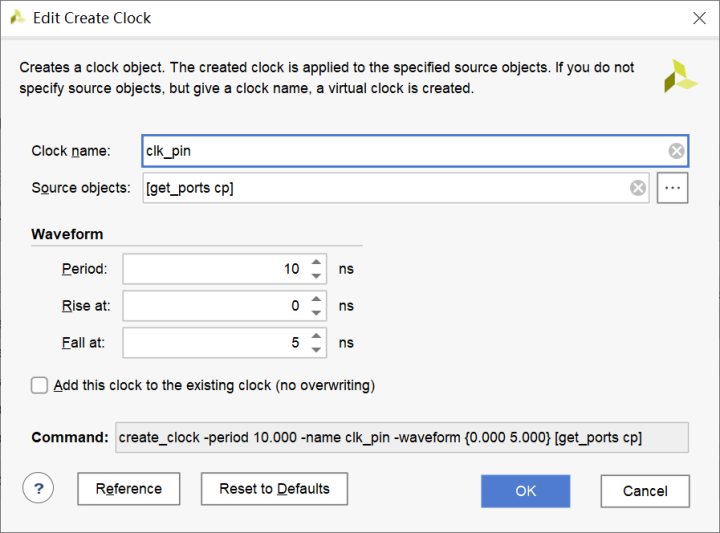

【c】双击左边Clock->Create Clock,进入Create Clock界面,在Clock name中输入clk_pin。在Source objects中选择右边的按钮。

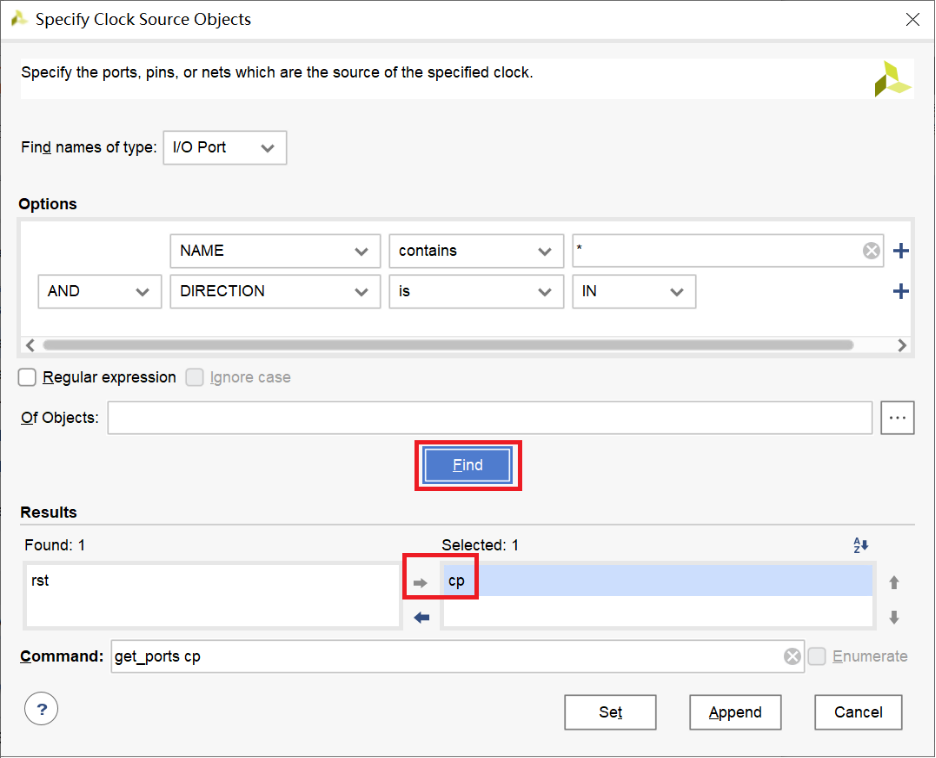

【d】在Specify Clock Source Object中Find names of type选择I/O Ports后点击Find,并将查找到的cp选中,如图:

完成选择后点击Set。对话框切换至如图:

点击ok完成时钟创建,结果参考下图:

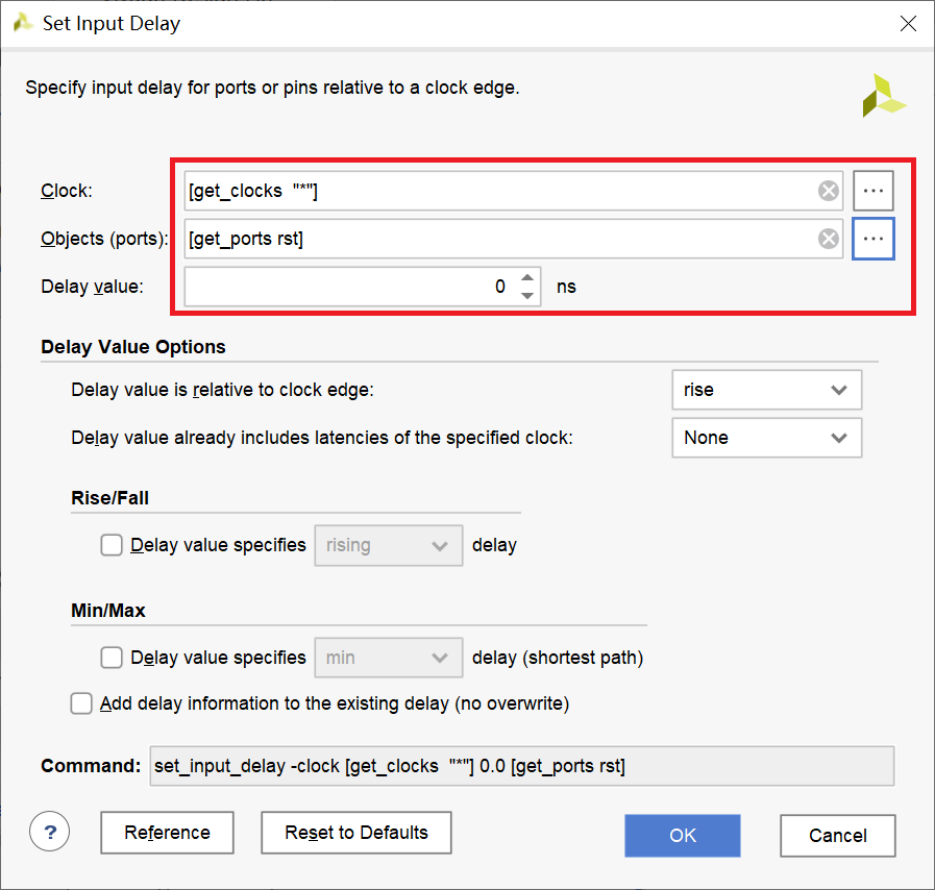

【e】设置Input Setup Delay ,双击左边Input->Input Setup Delay,如图:

进入Set Input Delay,按照下图配置:Clock选择clk_pin,Objects选择rst,Delay选择0 ns。完成设置后点击OK。

【f】接下来将设置Delay value specifies <min/max> delay,双击左边Input->Input Setup Delay。

将Clock选择为clk_pin、Objects选择rst、Delays value选择-0.5 ns、并选中Delay value specifies,

Delay设置成min。完成设置后点击ok。

【g】接下来设置Output Delay,双击左边Output->Set Output Delay。Clock选择clk_pin、Objects选择所有输出,Delay value设置为0ns。

【h】完成以上约束后可以在All Constraints看到如下约束结果。选择File->Save Constraints将设置的约束保存。

这时候如果打开Sources界面中的constraints,就可以看到XDC文件中增加了约束条件。

【i】在Flow Navigator中选择Synthesized Design ->Report Timing Summary。并将Options标签里将Path delay type设置成min_max。

再次综合后查看时序报告,如果在报告中看到有地方显示了红色,说明时序约束后,需求没有满足。然后在进行Implementation的时候,Vivado会自动优化布线路径,来满足用户设定的约束时间。如果在Implementation中还是显示无法满足,则需要分析电路进行进一步约束。